EAGLE: Lötstopmaske im Sony ES-Design

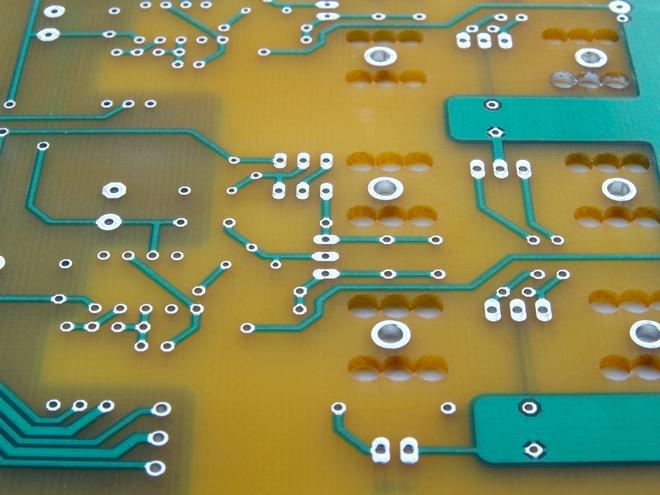

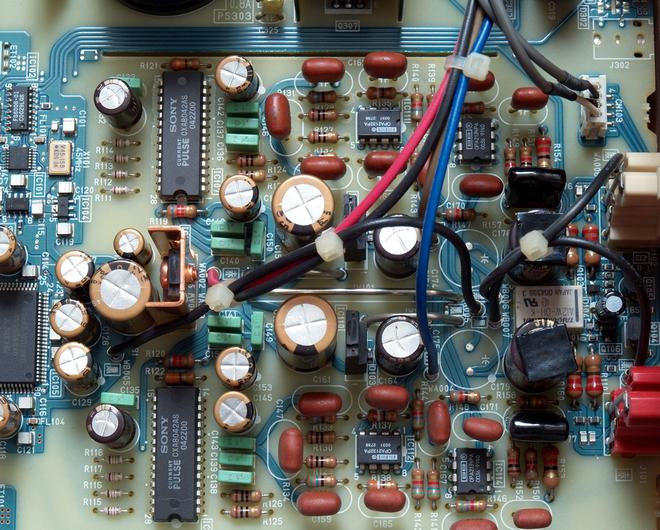

Habt ihr auch schonmal ein Gerät aus der ES-Serie auf gehabt und euch gefragt, warum Sony so am Lötstoplack „gespart“ hat? Ich schon. Und die einzige Erklärung, die mir eingefallen ist, ist: Es hat was! Das hat eben nicht jeder, es ist ein Stück weit individuell, einfach „mal anders“. Da kam mir dann spontan der Gedanke: Das will ich auch. Was die können, bekomme ich auch hin!

Also habe ich mich ans EAGLE gesetzt und etwas rumprobiert, um zu einem gefälligen Ergebnis zu kommen. Dabei bin ich etwas vom Original abgewichen, da Sony bei vielen Pads etwas gemacht hat, was das EAGLE nach meinem bisherigen Kenntnisstand nicht kann. Bei einer zweilagigen Platine sind die Pads nur auf der Seite in Kupfer ausgeführt, wo auch eine Leiterbahn dran ist; die andere Seite ist blank. Da ich selbiges eben nicht im EAGLE nachbilden konnte (ohne auf Pads zu verzichten und stattdessen Circles im entsprechenden Layer zu malen), wollte ich auch nicht um jedes Pad einen Ring aus Stoplack haben. Wer das selber doch lieber so haben möchte, kann das gerne tun. Dazu einfach in den Design Rules die Clearance-Werte nicht verändern.

Die Lötstopmaske erstellen

1.:

Das Layout muss fertig sein. Wenn du später noch eine Leiterbahn veränderst oder ein Bauteil verschiebst, musst du den ganzen Vorgang noch mal wiederholen. Natürlich kann man kleine änderungen auch von Hand vornehmen, aber das ist meistens gar nicht so einfach…

2.:

Zeichne ein Polygon genau auf dem Platinenrand entlang, ansonsten etwas darüber hinaus. Der Layer sollte dem entsprechen, für den die Stopmaske erstellt werden soll, also 1 – Top oder 16 – Bottom. Ich gehe hier mal beispielhaft von einer einseitigen Platine aus, also Layer 16. Vor dem Zeichnen solltest du „Orphans“ auf ein setzten, den „Rank“ auf 6 und „Width“ auf etwas kleines, z.B. 10mil bzw. 0.01 inch. Um es etwas übersichtlicher zu haben, gebe ich dem Polygon einen Namen, z.B. STOPBOTTOM.

3.:

Gehe in die „Design Rules“ und ändere folgende Werte:

- Im „Distance“-Tab: Copper/Dimension auf 0 mil (Standard: 40mil)

- Im „Clearance“-Tab:

Wire – Wire: 10mil (Standard: 8mil)

Wire – Pad: 0 mil (Standard: 8mil)

Wire – Via: 0 mil (Standard: 8mil)

4.:

Jetzt musst du mit „Ratsnest“ das Polygon freirechnen und kannst schonmal den Effekt bewundern. Falls auf dem Layer schon weitere Polygone vorkommen, zum Beispiel als Massefläche, kann es sein, dass diese nach den geänderten Design Rules nicht mehr richtig dargestellt werden (Abstände zu anderen Leiterbahnen und zum Platinenrand zu gering etc.). Dazu müssen bei den betroffenen Polygonen die „Isolate“-Werte entsprechend größer gemacht werden. Standard ist ja Null, wodurch das Minimum aus den Design Rules verwendet wird. Auch sollten alle Polygone einen höheren „Rank“ als 6 haben (also eine kleinere Zahl).

5.:

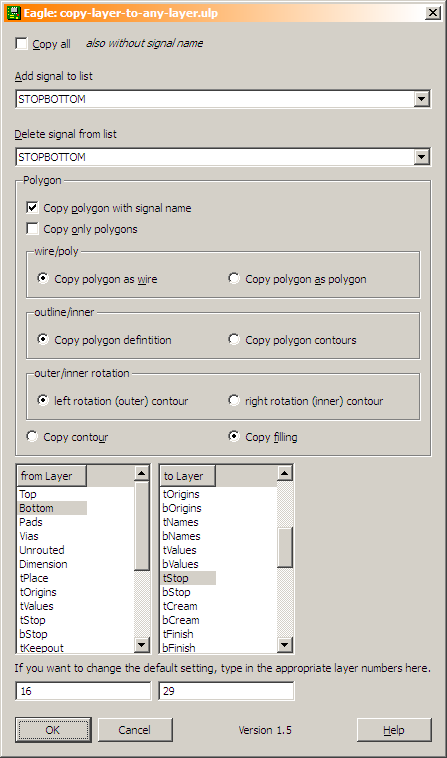

Starte das ULP mit dem Namen „copy-layer-to-any-layer.ulp“ und nehme die folgenden Einstellungen vor:

- In der Liste „Add Signal to list“ das Polygon auswählen, also STOPBOTTOM

- Einen Punkt bei „Copy polygon as wire“ setzen

- Einen Punkt bei „Copy filling“ setzen

- Bei „From Layer“ 1 oder 16 eintragen oder auf Top bzw. Bottom doppelklicken

- Bei „To Layer“ 29 oder 30 eintragen oder auf tStop bzw. bStop doppelklicken

- Alle anderen Einstellungen unverändert lassen, sonst klappt's nicht!

Wenn du jetzt auf OK klickst, kann es schonmal ein paar Sekunden dauern bevor was passiert. Das ist ein gutes Zeichen ;-). Es sollte ein kleines Fenster erscheinen, dass nicht viel mehr als zwei Buttons und eine Liste enthält, in der alle Befehle stehen, die das ULP soeben generiert hat. Da klickst du jetzt wieder auf „OK“ und dann heißt es – warten. Je nach Umfang der Platine kann es nämlich mehrere Minuten dauern, bis die Liste abgearbeitet ist. Dabei kann man schön zusehen, wie die einzelnen Linien von unten nach oben über das Board gezeichnet werden… Wenn der „Stop“-Knopf wieder grau ist, ist schon fast alles erledigt.

6.:

Jetzt musst du nur noch das Polygon im Signallayer löschen. Dazu am einfachsten mit gedrückter Umschalttaste auf STOPBOTTOM klicken und das ganze Polygon ist verschwunden.

Und damit sind wir auch schon fertig. Bei Jack & Al hat die Fertigung einer doppelseitigen Platine problemlos geklappt, andere Hersteller werden damit auch keine Probleme haben. :-)